模擬集成電路設計的藝術與科學

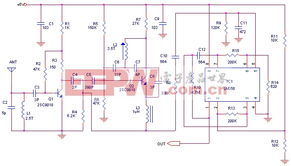

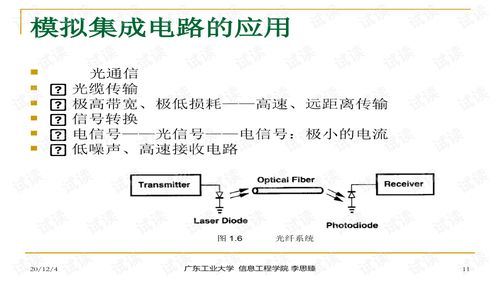

模擬集成電路設計是現代電子工業的基石之一,它專注于處理連續變化的信號,與處理離散0和1信號的數字集成電路相輔相成,共同構成了當今信息社會的硬件核心。從智能手機中的射頻收發器、音頻放大器,到醫療設備中的高精度傳感器接口,再到工業控制系統中的電源管理模塊,模擬集成電路無處不在,其性能直接決定了整個電子系統的效能、可靠性與能效。

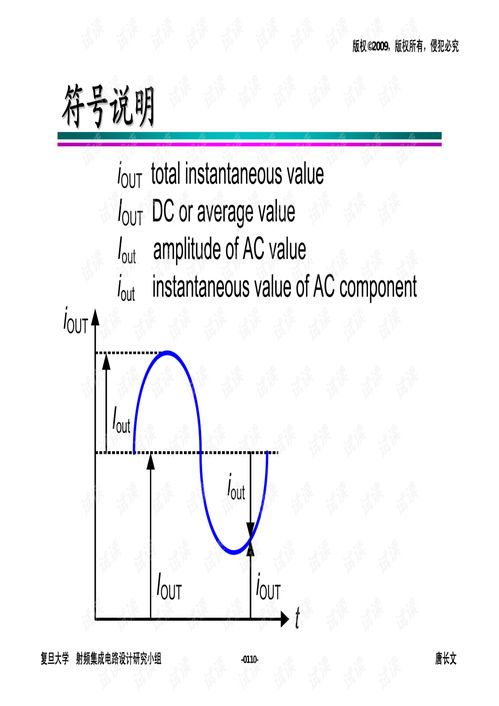

模擬集成電路設計的核心挑戰在于,它需要工程師在嚴格的物理約束下,實現精確、穩定且魯棒的性能。與數字設計可以依賴抽象的邏輯門和自動化工具不同,模擬設計更接近于一門藝術,需要深刻理解半導體器件的物理特性、電路拓撲結構以及工藝變異的影響。設計者必須綜合考慮增益、帶寬、噪聲、功耗、線性度、電源抑制比等一系列相互制約的性能指標。例如,提高運算放大器的速度往往意味著功耗的增加,而降低噪聲則可能需要更大的芯片面積。這種多目標優化過程,要求設計者具備深厚的理論功底和豐富的實踐經驗。

一個典型的模擬集成電路設計流程始于系統級定義與指標分解。明確芯片需要實現的功能、工作環境以及性能邊界后,設計進入電路級設計與仿真階段。在此階段,工程師選擇合適的電路架構(如差分對、電流鏡、共源共柵結構等),并利用SPICE等仿真工具,通過反復迭代來確定每個晶體管的具體尺寸、偏置條件等參數。版圖設計是緊隨其后的關鍵步驟,它將電路原理圖轉化為制造所需的物理幾何圖形。模擬版圖設計尤其講究,需要精心處理匹配、對稱、噪聲隔離、寄生效應(如寄生電容和電阻)以及電流密度等問題,任何微小的布局不當都可能導致芯片性能嚴重偏離仿真結果,甚至功能失效。

工藝角仿真和蒙特卡洛分析是確保設計魯棒性的重要手段。它們模擬制造工藝的波動(如晶體管閾值電壓、載流子遷移率的變化)對電路性能的影響,確保芯片在批量生產中,即使在最壞的工藝、電壓和溫度條件下,仍能滿足所有規格要求。

隨著工藝節點不斷向納米尺度演進,模擬集成電路設計面臨著新的機遇與挑戰。先進工藝提供了更高的器件密度和速度,但電源電壓的降低、短溝道效應加劇以及器件匹配性變差等問題,給傳統模擬電路設計方法帶來了巨大壓力。這促使了新設計技術的涌現,例如數字輔助模擬技術,利用數字校準和補償來彌補模擬性能的不足。系統級芯片(SoC)的普及,要求模擬設計者必須具備更強的系統思維,能夠與數字、射頻、軟件團隊緊密協作,實現模擬與數字域的協同優化。

總而言之,模擬集成電路設計是一個融合了深厚理論、精巧技藝和工程直覺的領域。它不僅是將物理原理轉化為實用功能的科學,更是在眾多約束中尋找最優解的創造性藝術。盡管挑戰重重,但正是這些挑戰,推動著技術的不斷進步,讓更高效、更智能、更互聯的電子世界成為可能。

如若轉載,請注明出處:http://m.xinntv.cn/product/86.html

更新時間:2026-03-29 04:46:25