單電源集成電路開關穩壓器的設計原理與實現分析

引言

在現代電子系統中,電源管理單元(PMU)是確保系統穩定、高效運行的核心。其中,開關穩壓器(Switch Mode Power Supply, SMPS)憑借其高效率、小體積和寬輸入電壓范圍等優勢,已成為集成電路(IC)電源設計的首選方案。特別是單電源輸入的開關穩壓器IC,因其設計簡潔、外圍元件少,被廣泛應用于便攜設備、嵌入式系統及各類消費電子中。本文將深入分析基于單電源的集成電路開關穩壓器的電路設計原理、關鍵模塊構成、性能考量以及設計挑戰。

一、 單電源開關穩壓器的基本原理

開關穩壓器的核心工作原理是利用功率開關管(通常為MOSFET)的高頻導通與截止,配合電感、電容等儲能元件,通過脈沖寬度調制(PWM)或脈沖頻率調制(PFM)來控制能量傳遞,從而實現高效的電能轉換與穩壓。

對于單電源設計,意味著整個IC僅需一個輸入電源(如電池或適配器輸出的直流電壓),通過內部電路產生所有必要的偏置電壓(如柵極驅動電壓、內部邏輯電源),并完成從輸入到期望輸出電壓的轉換。常見的拓撲結構包括:

- 降壓型(Buck):輸出電壓低于輸入電壓。這是應用最廣泛的拓撲。

- 升壓型(Boost):輸出電壓高于輸入電壓。

- 升降壓型(Buck-Boost):輸出電壓可低于或高于輸入電壓。

二、 集成電路內部關鍵模塊設計分析

一顆典型的單電源開關穩壓器IC集成了多個功能模塊,其協同工作是實現高性能的關鍵。

1. 功率級(Power Stage)

這是能量轉換的核心。在單片IC中,通常集成了:

- 功率開關管(Power MOSFET):包括上管(High-side)和下管(Low-side)。對于同步整流架構,兩者均為MOSFET;對于非同步架構,下管為肖特基二極管。設計時需在導通電阻(Rds(on))、開關速度、芯片面積和成本之間取得平衡。

- 柵極驅動器(Gate Driver):為功率管的柵極提供足夠強且快速的充放電電流,以減小開關損耗。驅動器本身需要一個高于輸入電壓的“自舉”(Bootstrap)電源來驅動上管,這是單電源設計中一個需要巧妙處理的問題。

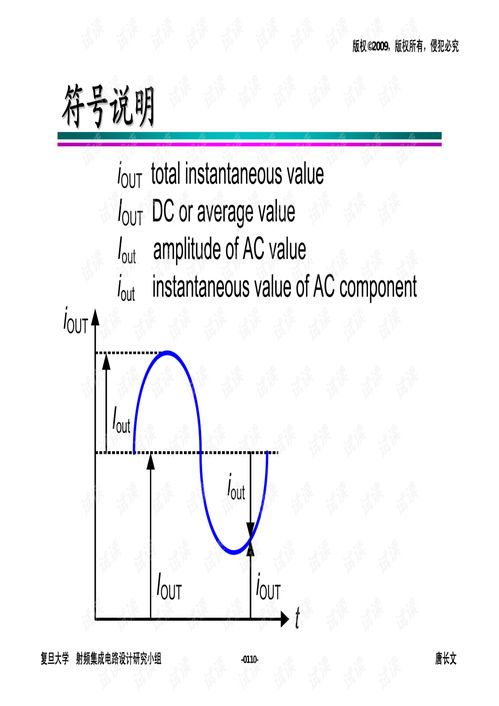

2. 控制與調制模塊

- 誤差放大器(Error Amplifier):將反饋電壓(通常來自輸出電壓的分壓)與內部精密基準電壓(如帶隙基準)進行比較,產生誤差信號。

- PWM/PFM調制器:根據誤差信號生成占空比可變的脈沖信號,控制功率管的開關。為兼顧輕載效率,現代IC常采用PWM/PFM自動切換模式。

- 振蕩器(Oscillator):產生恒定頻率的鋸齒波或時鐘信號,作為PWM的時基。頻率選擇(通常在數百kHz至數MHz)需權衡效率、體積(外圍電感電容大小)和電磁干擾(EMI)。

3. 保護與輔助電路

- 過流保護(OCP):通過檢測下管電流或電感電流峰值,防止芯片和負載損壞。

- 過溫保護(OTP):集成溫度傳感器,在結溫過高時關閉輸出。

- 欠壓鎖定(UVLO):確保輸入電壓達到一定閾值后芯片才啟動,防止工作異常。

- 軟啟動(Soft-start):控制啟動時的占空比緩慢增加,抑制輸入浪涌電流。

- 內部低壓差線性穩壓器(LDO):為芯片內部的模擬和數字電路(如基準、誤差放大器、邏輯控制)提供一個干凈、穩定的低壓電源,通常由輸入電壓或輸出電壓衍生而來。

三、 單電源設計的特殊考量與挑戰

1. 自舉電源的生成

在降壓拓撲中,驅動上管NMOS需要柵極電壓高于源極電壓(即開關節點電壓)。單電源下,通常采用“自舉電路”:利用一個二極管和電容,在下管導通期間,從輸入電源(VIN)或內部LDO輸出(VCC)為電容充電,從而在上管需要導通時提供一個浮動的驅動電壓(VBS)。該電路的設計直接影響高壓側驅動的可靠性和效率。

2. 高效率與低靜態電流的平衡

對于電池供電設備,輕載和待機效率至關重要,這就要求控制電路本身的靜態電流(Quiescent Current, IQ)極低。這給模擬電路(如基準源、誤差放大器)的設計帶來了挑戰,需要在極低功耗下仍保持良好的精度和響應速度。

3. 熱管理與封裝

功率損耗(主要是開關管導通損耗和開關損耗)會導致芯片溫升。在單芯片集成中,必須精心規劃功率管、驅動器和控制電路的版圖布局,優化散熱路徑。封裝的選擇(如QFN、DFN等具有裸露焊盤(Exposed Pad)的封裝)對散熱性能影響巨大。

4. 電磁兼容性(EMI)抑制

開關動作產生的高頻di/dt和dv/dt是主要的EMI源頭。在IC內部設計中,可以采用:

- 柵極驅動斜率控制,減緩開關邊沿。

- 擴頻調制技術,將開關能量分散在更寬的頻帶上。

- 優化的功率回路版圖布局,最小化寄生電感。

四、 設計流程與仿真驗證

現代開關穩壓器IC的設計是一個高度系統化的過程:

- 系統定義:明確輸入電壓范圍、輸出電壓/電流、效率目標、保護功能等規格。

- 拓撲選擇與電路設計:確定功率級參數(電感、電容計算)、設計各個模擬和數字模塊的子電路。

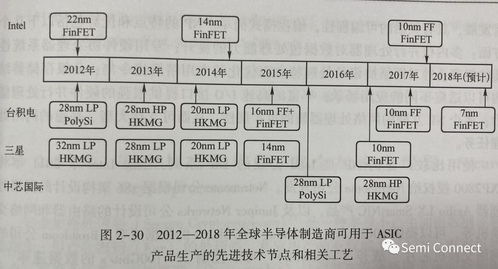

- 晶體管級實現與版圖設計:使用CMOS或BCD工藝,進行器件選型、電路繪制,并特別關注功率路徑、敏感模擬信號(如反饋、基準)的隔離與屏蔽。

- 綜合仿真驗證:利用SPICE等工具進行直流、交流、瞬態、蒙特卡洛以及溫度掃描仿真,驗證功能、效率、負載調整率、線性調整率、瞬態響應等關鍵指標。

- 樣片測試與迭代:流片后在實際PCB上進行全面測試,評估其真實性能,并根據結果進行設計優化。

結論

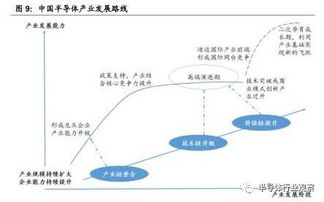

單電源集成電路開關穩壓器的設計是模擬與功率集成電路領域的經典課題。它要求設計者深刻理解開關電源原理、半導體器件特性、模擬電路設計以及熱力學和電磁學知識。隨著工藝進步(如更先進的BCD工藝)和設計技術發展,未來的單電源開關穩壓器IC將朝著更高效率(尤其是輕載效率)、更高功率密度、更高集成度(集成更多功率管、甚至電感)、更智能的數字控制以及更優越的EMI性能方向持續演進,為日益復雜和節能的電子系統提供強勁而精密的“心臟”。

如若轉載,請注明出處:http://m.xinntv.cn/product/97.html

更新時間:2026-04-11 21:57:46